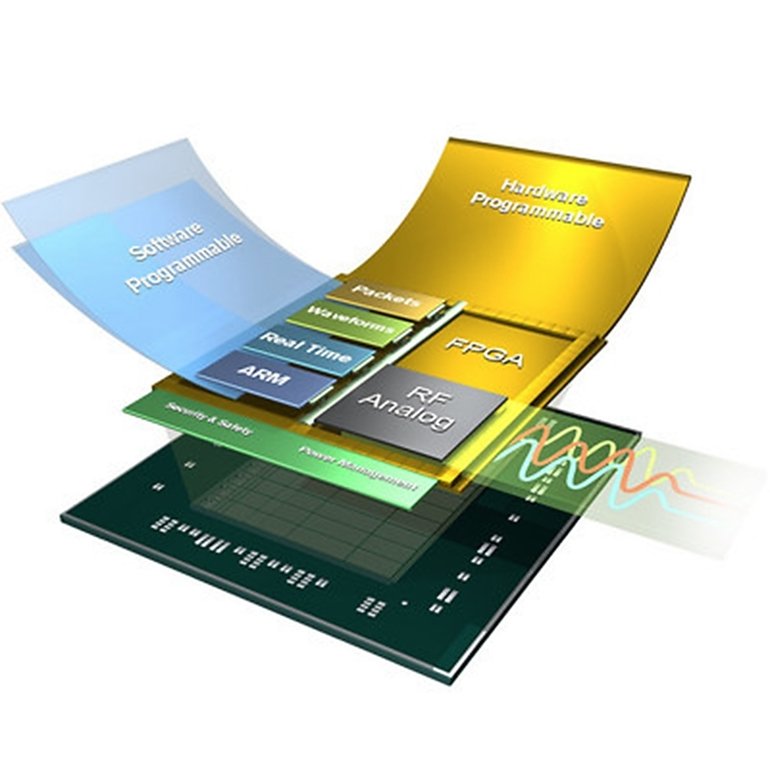

Xilinx Inc. meldete Anfang Oktober die ersten Auslieferungen seiner Zynq-Ultrascale-RFSoc-Familie, deren Architektur die HF-Signalkette in einem Soc integriert. Dies ist ein Technologie-Durchbruch im Hinblick auf Anwendungen für 5G-Wireless, Cable-Remote-Phy und Radar. Auf der Basis der 16-nm Ultrascale+MPSoc-Architektur bieten diese All-Programmable-RFSocs die monolithische Integration der HF-Datenkonverter mit 50- bis75-fachen Gewinn an Systemleistung und Footprint-Reduzierung. Durch SD-FEC (Soft-Decision Forward Error Correction) erfüllen sie dabei die 5G- und DOCSIS-3.1-Standards. Mit der Auslieferung der ersten Samples an zahlreiche Kunden ist die Zynq-Ultrascale-RFSoc-Familie ab sofort im Xilinx-Early-Access-Program verfügbar. Die Zynq-RFSocs kombinieren die HF-Datenwandler und SD-FEC-Kerne mit High-Performance 16-nm Ultrascale programmierbarer Logik und ARM-Mehrprozessorsystem. Sie bilden damit eine durchgehende Analog-auf-Digital-Signalkette. Während die HF-auf-Digital Signalaufbereitung und -verarbeitung in Stand-Alone-Subsysteme segmentiert wird, vereinigen die Zynq-Ultrascale-RFSocs das analoge, digitale und eingebettete Software-Design in einem monolithischen Baustein und erzielen damit robuste Systeme. Die von der Zynq-RFSoc-Familie angesprochenen Einsatzfelder umfassen entfernte Funkleitstellen (radio heads) für Massive-Mimo, mobiles Backhaul für Millimeterwellen, 5G-Baseband, drahtloser Festnetzzugang, Remote-Phy-Nodes für Kabel-TV, Radar, Test und Messtechnik, Satcom und Milcom/Airborne Radio und weitere High-Performance HF-Applikationen. Samples der Zynq-Ultrascale-RFSoc-Bausteine werden bereits ausgeliefert. Auch der Zugriff auf die Vivado-Design-Suite mit Unterstützung der Zynq-Ultrascale-RFSoc-Bausteine ist ab sofort verfügbar. Kunden, die am Zynq-Ultrascale-RFSoc-Early-Access-Program interessiert sind, können ihren lokalen Xilinx-Repräsentanten kontaktieren. jke